Persönliches, subjektives Kursfazit

Computersysteme, aka technische Informatik. Warum die Vorlesung umbenannt wurde, keine Ahnung. Im Moment fällt es mir jedoch schwer ein Fazit zu ziehen, da ich noch keine Klausurergebnisse habe.

Literatur-empfehlung

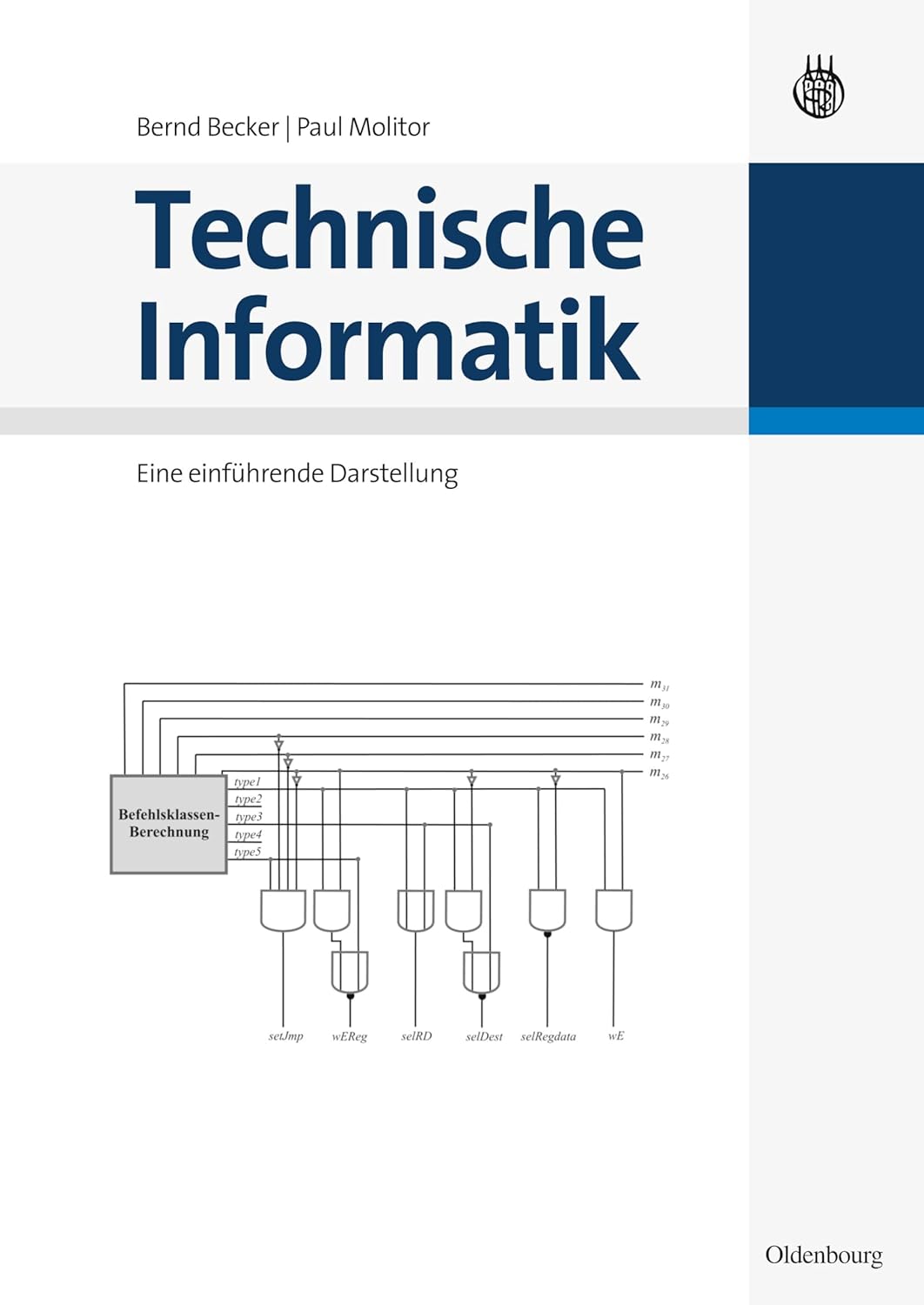

Das 1. Buch von Becker und Molitor hat mir durchaus an einigen Stellen von CS1 geholfen (wer keins mehr findet, kann das von Vossen nehmen. Sie überschneiden sich). Für CS2 hatte ich keine Zusatzliteratur in Papierform, da google doch ziemlich viele Informationen zum Thema ausgespuckt hat. Das 2. Buch von Dr. Bähring (Kursleitung CS2) sollte man sich anschauen und die Übungen machen. Es kann durchaus sein, dass die ein oder andere Übungsaufgabe ihren Weg in der Klausur findet. Leider trifft die 2 Sterne-Rezension des Buches bei Amazon.de durchaus zu, was die Fehler angeht. Gleiches gilt für die anderen Unterlagen von Hr. Dr. Bähring. Dort haben sich auch einige Fehler eingeschlichen, die das Verständnis der Thematik sehr erschweren. Ärgerlich, aber menschlich. Denke jedoch, dass die in den nächsten Semestern ausgemerzt werden.

Klausurbewertung und Organisatorisches

Derzeitiger Stand (SS2010, ohne mein Ergebnis zu wissen): WOW! Stellt euch vor, ihr könnt jedes Thema im Kursskript korrekt wiedergeben und einem Mitstudenten richtig erklären, Transferleistung erbringen, wart auf beiden Studientagen und könnt alle ehemaligen Klausuren, sowie Einsendeaufgaben und Studientagsaufgaben selbstständig und innerhalb der Zeitvorgabe nach der eigenen Klausurvorbereitung lösen. Das nennt man doch „gute Vorbereitung“, geht mit einem guten Gefühl zu Klausur und freut sich auf die 1.x-2.x, oder? Dieses Semester bin ich froh, wenn ich bestanden habe. Leider hat sich der Lehrstuhl, meiner Meiner Meinung nach, im CS2-Teil der Klausur deutlich verkalkuliert. Die geforderte Transferleistung ist in den 1.5 Stunden Klausurzeit absolut nicht zu erbringen gewesen. Eine Stunde mehr wäre angebracht, wie ich finde. Ich dachte zwar zunächst, dass ich einfach „zu blöd“ bin, es ist aber der allgemeine Tenor in der NG. Oder wir waren alle „zu blöd“… warten wir das Ergebnis also erstmal ab.

Update: das Ergebnis ist nun da. Schlecher als erhofft, besser als erwartet. Durchschnittsnote der Klausur ist 3,5. Nicht bestanden haben – trotz der um 15% gesenkten Punktgrenze – knapp 30%. Von der anderen Seite aufgerollt ergeben sich 17%, welche zwischen 1,0 (7%) und 2,0 (10%) liegen. Ich darf mich, netter Weise, zu den 10% zählen und bin froh die technische Informatik nun abhaken zu können. Auch wenn sie mir durchaus Spaß gemacht hat.

Die Betreuung in der Newsgroup ist mehr als gut. Der Kursbetreuer (und auch Profs greifen manchmal ein) ist aktiv, Mitstudenten helfen bei Fragen gerne weiter. Qualität der Studientage war außerordentlich. Würde jedem raten beide Studientage zur technischen Informatik zu besuchen oder zumindest die dort behandelten Aufgaben gewissenhaft zu studieren.

Kursinhalt Computersysteme 1

technische Informatik A

Kurseinheit 1

Hier geht es um Schaltfunktionen und Boolsche Ausdrücke: Mengen, Graphen, Einsetzungen, Identitäten, Lösen von Gleichungen und Ungleichungen, Kosten, (kanonische) DNF/KNF, etc. Darstellungssatz und Minimalpolynome (Primimplikanten, Bestimmung Minimalpolynome), KV Diagramme, Quine Mc Cluskey und Unverfügbarkeit von Systemen.

Kurseinheit 2

Schaltnetze, rechnen mit Schaltnetzen, Einsetzungen und Identitäten, Konstruktionen von Schaltnetzen zu Polynomen, Komplexitätsmaße (Tiefe, Kosten, etc), deren Beweis über Induktion, Zahlendarstellungen (Komplementdarstellung, IEEE754, etc.), arithmetische Operationen auf binären Mengen, MUX/DEMUX, Schaltnetze für Ganzzahl-Arithmetik (HA, FA, n-bit Carry Chain, Conditional Sum, Multiplizierer).

Kurseinheit 3

Speicherglieder (SR Latches mit NAND/NOR) und Zeitverhalten (takt(flanken)gesteuert, etc.), Setz- und Haltezeiten, Flipflops (JK-, Master/Slave-, D-), Ein- und Zweiflankensteuerung, charakteristische Gleichungen, Zustandsgraphen, ladbare (Schiebe-)Register, Auomatenmodelle (Mealy/Moore), Überführung und Äquivalenz, Rückkopplungsbedingungen, Analyse und Synthese von Schaltwerken, Zustands-Minimierung mittels Äquivalentklassen, Zustands-Codierung (Hot-One, Zusammengesetzt), programmierbare Logikbausteine (ROM, PROM, (E)EPROM, PAL, PLA), Mikroprogrammsteuerwerke.

Kurseinheit 4

Komplexe Schaltwerke, RTL Notation, Steuer- und Operationswerke, ASM Diagramme und Blöcke, sowie Konstruktionsregeln. Entwurf von Steuerwerken, Lösungen mit Mealy und Moore, Mikroprogrammierte Steuerwerke, Rechenwerke, Leitwerke, Datentransfer zwischen CPU und Speicher, ALU und Verzweigungsbefehle, Speicher, interne und externe Busse, Prozessorregister, Stackpointer und Unterprogramme, Interrupts und Interrupt-Controller, Datenpfade, Schiebemultiplexer, logische Operationen, Statusflags, Mikrobefehlsformat, Adresserzeugung, Speicher-Erweiterungen und Organisation.

Kursinhalt Computersysteme 2

technische Informatik B

Kurseinheit 1

Rechnerarchitektur, Moor’sches Gesetz, CISC/RISC, Skalarität, Superskalarität, VLIW und EPIC, statisches Scheduling, Befehlssatzarchitekturen, Datenformate (Halbwort, Double, BCD, …), Adressraumorganisation, Big- und Little Endian, Befehlssatz (Gleitkomma, Steuerbefehle, …) und Format (Register/Register, Register/Speicher, Stack, Akkumulator), Adressierungsarten (Unmittelbar, Direkt, Indirekt, Registerindirekt, etc.), RISC und CISC Prinzipien, Beispiele für RISC, DLX Architektur, Assemblerbefehle, Grundlegender Aufbau der Prozessorkerne, Pipeline-Prinzip, Befehls-Pipelining, DLX Pipeline (IF, ID, EX, MEM, WB) und ihre Implementierung, Pipeline-Konflikte (echt, unecht: RAW, WAR, WAW, …), Daten-, Gegen-, und Ausgabeabhängigkeiten, Steuerflusskonflikte und Lösungen (NOP, Forwarding, Interlocking, Übertaktung, Registerumbebennung, etc.), Sprungzieladresscache (BTAC, BTB), dynamische und statische Sprungvorhersage, Abhängigkeitsgraphen.

Kurseinheit 2

Grundtechniken heutiger Prozessoren, von skalar zu superkalar, Komponenten des superskalaren Prozessors, superkalare Pipeline, in-order und out-of-order Ausführung, Instruction Window, Umordnungspuffer, Commitment, etc. Details der VLIW und der EPIC Technik, Vergleich von Superskalar und VLIW/EPIC. Chipsätze und IO. Details Superskalartechnik. Trace- und I-Cache, spekulative Ausführung, Ein- Zwei-bit Prädiktoren (Hystrese und Sättigung, BHT), Korrelationsprädiktoren (BHR+PHT), Details der Registerumbenennung, Befehlszuordnungsstrategie, Issue/Dispatch, Ausführungsstufen, Multimediaeinheiten, Gewährleistung sequentielle Programmsemantik und präzise Unterbrechungen, TLB und Rückordnung(spuffer).

Kurseinheit 3

Speicherverwaltung und innovative Techniken (zeitliche und räumliche Lokalität), Speicherhierarchie, Register und Registerfenster, sowie Over- und Underflow bei Registerfenstern und deren Behandlung, virtuelle Speicherverwaltung (logische und physikalische Speicheradressen), Pagefaults, Verdrängungs- und Auslagerungsstrategien (optimal, (Pseudo-)LRU, etc.), Code- und Datencache (Aufbau und Organisation), Trefferrate und Misses, VA-Cache, Direct Matched und n-fach Satzassoziativ (Vorteile, Nachteile, Aufbau), Cache-Flattern, Verringern des fehlzugriffs, Preloading und Compiler-Optimierungen, L1, L2, virtueller Cache, Kohärenz und (sequentielle) Konsistenz, MESI (die 4 Statusbits, Funktion, Implementierung), Stand und Grenzen der Technik, Erhöhung Durchsatz und (simultane) Mehrfädigkeit, Multicore, VLSI, Cycle-by-cycle und Block (statisch, dynamisch) Interleaving, horizontaler und vertikaler Verlust.

Kurseinheit 4

Benchmarking (MIPS und MFLOPS), parallele Systeme, Berechnung Transferzeit, Übertragung, Kommunikationszeit, SpeedUp, absolut und relativ, Skalierung, Mehraufwand durch Kommunikation der Prozesse, sowie Auslastung, Parallelindex, Amdahls Law, Synergieeffekte, Verbindungssturkturen, statische (Ring, chordaler Ring, Stern, …) und dynamische Netze (Mehrfachbus, Speicherkopplung – UMA/NCC-CC-NUMA, COMA), Durchschaltevermittlung, Wegefindung, virtual Cut through, (buffered) Wormhole, Multicore und Schaltnetzwerke, Permutationsnetze, Cache-Kohärenz und Speicherkonsistenz, Modelle, Non-Blocking, Dekkers Algorithmus, DSM-Multicore, Thrashing (Flattern aus dem letzten Kapitel), nachrichtengekoppelte Multicore-Systeme (1st, 2nd, 3rd Generation), verteilte Systeme und Cluster/Workstation Farmen, Clustering Details.

Buchempfehlung